- 您现在的位置:买卖IC网 > Sheet目录342 > MCM69C432TQ20 (Freescale Semiconductor)IC CAM 1MB 50MHZ 100LQFP

�� �

�

Freescale� Semiconductor,� Inc.�

�INTERRUPT� BIT� DEFINITIONS�

�INSTRUCTION� SET� DETAILS�

�Bit� 0:�

�Bit� 1:�

�Bit� 2:�

�Bit� 3:�

�Bit� 4:�

�Bit� 5:�

�1� =� Enable� interrupt� on� insert� with� full� entry�

�queue�

�1� =� Enable� interrupt� on� insert� with� full� table�

�1� =� Enable� interrupt� on� completion� of�

�CHECK–FOR–VALUE� instruction�

�1� =� Enable� interrupt� on� completion� of�

�INITIALIZE–TABLE� instruction�

�1� =� Enable� interrupt� on� failed� attempt� to� enter�

�fast–entry� mode�

�1� =� Enable� interrupt� on� CAM� table� reaching�

�The� MCM69C432� is� prepared� for� match� operations� by�

�writing� data� and� instructions� via� the� control� port.� In� the� gen-�

�eral� case,� required� data� is� loaded� into� I/O� registers� 0� –� 3,�

�then� an� instruction� is� issued� by� writing� an� operation� code� to�

�the� operation� register.� As� a� result� of� running� an� instruction,�

�the� CAM� table� can� be� modified,� bit(s)� can� be� set� in� the� flag�

�register,� error� codes� can� be� returned� in� the� error� code� regis-�

�ter,� and� an� interrupt� can� be� generated� if� enabled.� For� a� par-�

�ticular� condition� to� generate� an� interrupt,� the� interrupt�

�register� bit� specific� to� that� condition� must� be� set.� The� user�

�C.�

�N� section� for� any� exceptions.�

�Simultaneous� Port� Operations� I�

�,�

�OR�

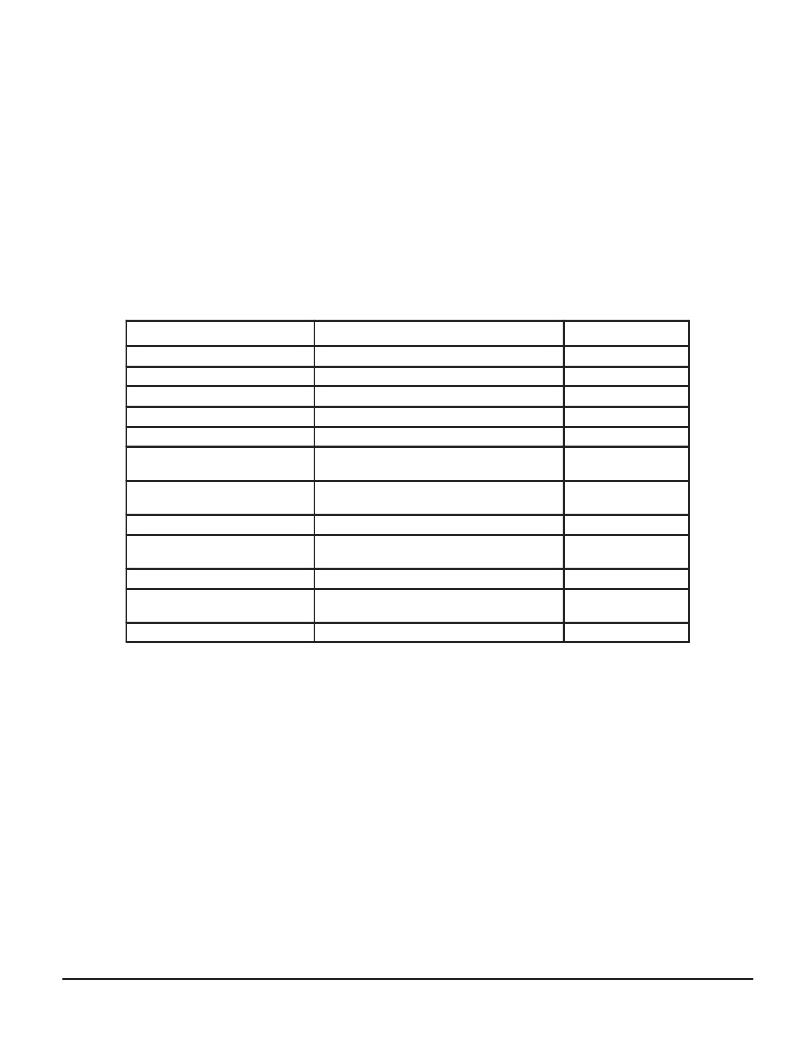

�Table� 1.� MCM69C432� Operation� Summary� C�

�D�

�ON�

�IC� table�

�M�

�E� CAM� table�

�LE� via� the� control� port�

�CA�

�EE�

�S�

�FR� entry� mode� suited� for� simultaneous� loading�

�BY� and� matching�

�VE�

�I�

�CH�

�A�

�Bit 6:�

�Bit� 7:�

�almost–full� point� should� verify� that� the� last� operation� complete� bit� (bit� 10)� of�

�1� =� Enable� interrupt� on� fast� read� with� non–empty� the� flag� register� is� set� before� executing� the� next� instruction,� if�

�queue� the� instruction� just� executed� modifies� I/O� registers.� See� the�

�1� =� Enable� interrupt� on� illegal� instruction�

�Operation� Description� OP� Code� (Base� 16)�

�INSERT� VALUE� Loads� a� new� entry� into� the� CAM� 0000� or� 000F�

�S�

�DELETE� VALUE� Removes� an� entry� from� the� 0001� or� 000E�

�CHECK� FOR� VALUE� Runs� a� match� cycle� 0006�

�INITIALIZE� TABLE� Prepares� CAM� table� for� matching� 000B�

�FAST–ENTRY� MODE� Selects� entry� mode� suited� for� initial� CAM� table� load� 0004�

�BUFFERED–ENTRY� MODE� Selects� 0005�

�D�

�SET� ATM� MODE� Enter� mode� that� provides� concurrent� VPC/VCC� 0008�

�search�

�R�

�RETURN� ENTRY� COUNT� Determines� number� of� entries� in� CAM� 0003�

�U�

�T�

�SET� GLOBAL–MASK� REGISTER�

�SET� ALMOST–FULL� POINT�

�SET� FAST–READ� REGISTER�

�FAST� READ�

�Determines� match� bits� to� be� checked� in� a� match�

�operation�

�Defines� CAM� almost–full� condition�

�Defines� table� entry� that� is� output� by� the� fast–read�

�operation�

�Outputs� one� CAM� table� entry�

�0002� or� 000D�

�0007�

�0009�

�000A�

�INSERT� VALUE�

�This� instruction� is� used� to� load� a� new� match/output� value�

�into� the� CAM.� The� contents� of� I/O� registers� 0� –� 3� are� con-�

�catenated,� with� bit� 15� of� register� 3� as� the� most� significant� bit,�

�and� bit� 0� of� register� 0� as� the� least� significant� bit.�

�If� the� MCM69C432� is� running� in� the� buffered–entry� mode,�

�the� resulting� 64–bit� value� is� written� to� the� first� available� loca-�

�tion� in� the� entry� queue,� and� is� immediately� available� for�

�matching.� If� a� buffered� insert–value� instruction� is� attempted�

�when� the� entry� queue� is� full� (indicated� by� bit� 5� of� the� flag� reg-�

�ister� =� 1),� no� value� is� written,� an� error� code� of� FFF816� is�

�returned� in� the� error� code� register,� and� the� error–condition�

�flag� (bit� 7)� is� set� in� the� flag� register.� An� interrupt� is� generated,�

�if� enabled� by� bit� 0� of� the� interrupt� register� being� set.�

�If� the� MCM69C432� is� running� in� the� fast–entry� mode,� the�

�concatenated� 64–bit� value� is� written� directly� to� the� CAM�

�array.� If� an� insert–value� instruction� is� attempted� when� in�

�fast–entry� mode� and� the� table� is� full,� no� value� is� written,� an�

�error� code� of� FFF916� is� returned� in� the� error� code� register,�

�and� the� error–condition� flag� (bit� 7)� is� set� in� the� flag� register.�

�(The� table–full� condition� is� indicated� by� bit� 6� of� the� flag� regis-�

�ter� being� set.)� An� interrupt� is� generated,� if� enabled� by� bit� 1� of�

�the� interrupt� register� being� set.�

�Only� one� entry� is� allowed� for� a� given� match� pattern.� If� an�

�entry� is� made� in� the� table� that� duplicates� an� existing� match�

�pattern,� it� will� overwrite� the� entry� already� in� the� CAM� table,� if�

�the� CAM� is� in� buffered–entry� mode.� The� user� must� ensure�

�that� no� entries� with� the� same� match� pattern� are� inserted� in�

�fast–entry� mode.�

�DELETE� VALUE�

�This� instruction� is� used� to� remove� a� match/output� value�

�from� the� CAM.� The� contents� of� I/O� registers� 0� –� 3� are� con-�

�catenated,� with� bit� 15� of� register� 3� as� the� most� significant� bit,�

�and� bit� 0� of� register� 0� as� the� least� significant� bit.� The� bits� that�

�have� a� 0� in� the� corresponding� bit� of� the� global–mask� register�

�are� used� to� find� a� matching� entry� in� the� CAM� table.� If� such� an�

�entry� is� found,� it� is� invalidated.� Note� that� any� bit� that� is� not� a�

�MCM69C432� ?� SCM69C432�

�8�

�For� More� Information� On� This� Product,�

�Go� to:� www.freescale.com�

�MOTOROLA� FAST� SRAM�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MCP1401T-E/OT

IC MOSFET DRVR INV 500MA SOT23-5

MCP1403T-E/MF

IC MOSFET DRIVER 4.5A DUAL 8DFN

MCP1406-E/SN

IC MOSFET DVR 6A 8SOIC

MCP14628T-E/MF

IC MOSFET DVR 2A SYNC BUCK 8-DFN

MCP14700T-E/MF

IC MOSFET DRIVER HIGH/LOW 8DFN

MCP14E3T-E/MF

IC MOSFET DVR 4.0A DUAL 8DFN

MCP14E6T-E/MF

IC MOSFET DRIVER 2A 8DFN-S

MCP14E9T-E/MF

IC MOSFET DRIVER 3A 8DFN-S

相关代理商/技术参数

MCM69C432TQ20R

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:16K x 64 CAM

MCM69C433

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:16K x 64 CAM

MCM69C433TQ15

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:16K x 64 CAM

MCM69C433TQ15R

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:16K x 64 CAM

MCM69D536

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:32K x 36 Bit Synchronous Dual I/O, Dual Address SRAM

MCM69D536TQ6

制造商:Motorola Inc 功能描述:Synchronous SRAM, 32K x 36, 176 Pin, Plastic, QFP

MCM69D536TQ6R

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:32K x 36 Bit Synchronous Dual I/O, Dual Address SRAM

MCM69D536TQ8

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:32K x 36 Bit Synchronous Dual I/O, Dual Address SRAM